AI PIM

Technical Features

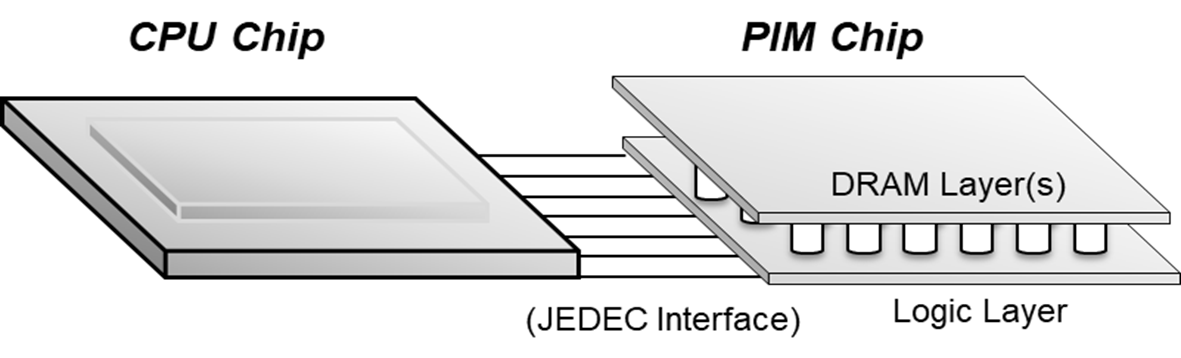

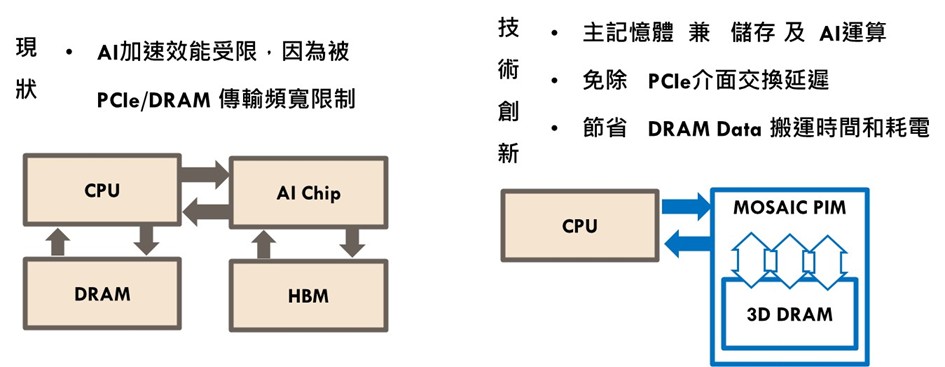

3D stacked AI PIM breaks through generative AI bottlenecks by integrating AI compute into memory, achieving 8x higher bandwidth and 90% lower energy consumption. It supports JEDEC-standard interfaces and seamlessly accelerates edge AI applications.

Technical Description

AI PIM leverages advanced 3D stacking technology to reduce data transmission distances from micrometers to nanometers, effectively overcoming memory and transfer bottlenecks in generative AI GEMV operations and expanding the scope of AI applications. By adopting a Process in/near Memory (PINM) architecture, the solution tightly integrates computing logic with memory, combined with IC design and value-added memory manufacturing, helping Taiwan’s memory industry establish market leadership in AI applications. In terms of performance, it achieves 8x increase in generative AI processing speed, a 90% reduction in energy consumption and significant cost savings. With JEDEC-standard interfaces, it further accelerates AI chip deployment across edge and end devices. On the supply side, it complements costly HBM solutions, mitigates production gaps in silicon interposers, and enables application niches for mature semiconductor processes. By collaborating with small and medium-sized IC design houses and startups, it promotes AI chip adoption in portable and edge markets, enhances supply chain resilience, injects new growth momentum into Taiwan’s AI and memory industries, and strengthens global competitive advantages.

Photos

Contact

Name:王耀宗

Phone:03-5913316

E-mail:victor.wang@itri.org.tw